|

|

|

Products > Discontinued Products > VECP Starter Kit (Xilinx ZU3EG) > VECP Starter Kit

Products > Discontinued Products > VECP Starter Kit (Xilinx ZU3EG) > VECP Starter Kit |

| |

|

VECP Starter Kit |

- Xilinx Zynq UltraScale+ ZU3EG MPSoC based on 1.2 GHz Quad Arm Cortex-A53 and 600MHz Dual Cortex-R5 Cores

- 4GB DDR4, 4GB eMMC, 128MB QSPI Flash

- 1 x USB 3.0 Host, 1 x USB 3.0 Device, 1 x USB-UART, 2 x Gigabit Ethernets, MIPI-CSI, HDMI, TF…

- SONY imx334 4K Sensor

- Ready to Run Linux OS

- 4k/30fps Image Signal Processing IP Core

- GigE Vison 2.0 IP Core

- Machine Vision USB3 Vision IP Core

|

|

|

|

| |

|

MYIR is a Xilinx Alliance Member, welcome to use MYIR's Xilinx products!

We also offer custom design services, welcome your inquiry!

http://www.xilinx.com/alliance/memberlocator/1-2wv1bc.html

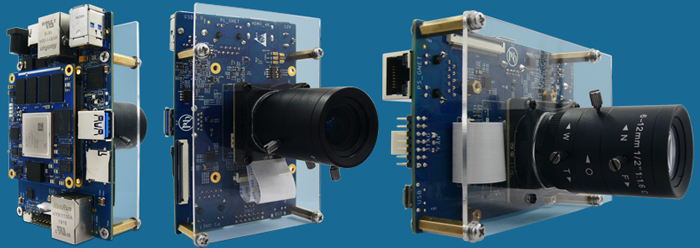

The VECP

Starter Kit is an affordable and complete Vision

Edge Computing Platform to provide an

excellent image processing solution for computer vision development based

on Xilinx Zynq

UltraScale+ ZU3EG MPSoC which

features a 1.2 GHz quad-core ARM

Cortex-A53 64-bit application

processor, a 600MHz dual-core real-time ARM

Cortex-R5 processor, a Mali400

embedded GPU and rich FPGA fabric. The kit comes with a MYD-CZU3EG-ISP development board and

some necessary cable accessories to help users start their development rapidly.

The MYD-CZU3EG-ISP development board is capable of handling 4K video at 30fps through

the built-in ISP core and can implement ultra-low delay video transmission at maximum

0.7ms. The input videos support Bayer, YCbCr

and RGB formats to meet the demand of

high frame rate and high-resolution image acquisition. The image can be output

through diversified image output interfaces including HDMI, Gigabit Ethernet and USB 3.0. The integrated GigE vision

IP core supports Machine Vision GenICam V2.4.0 standard and user-defined XML files. The USB3 vison IP core also meets the industrial

machine vision standard.

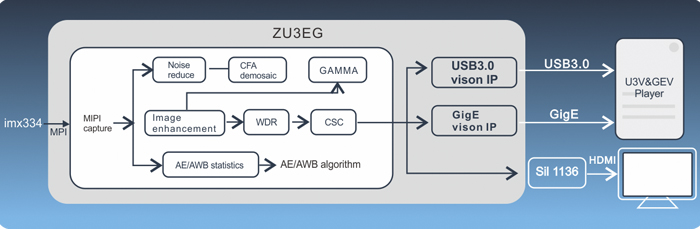

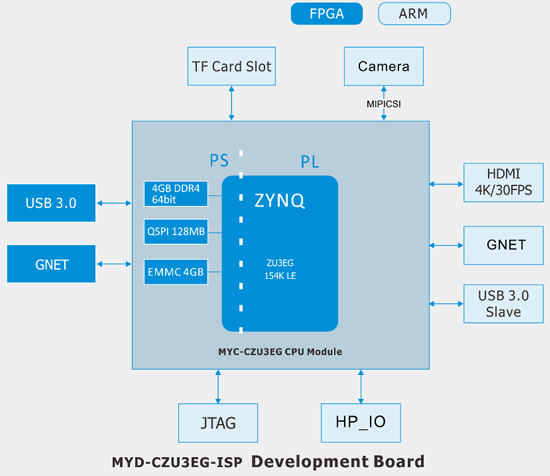

VECP Data Processing Frame

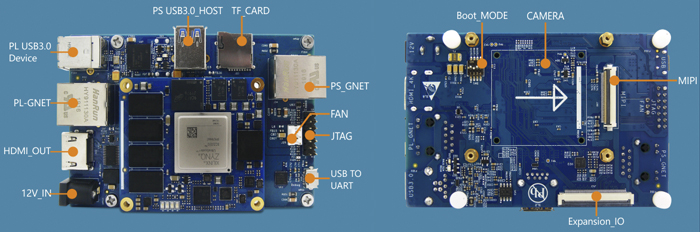

The MYD-CZU3EG-ISP development board consists of a MYC-CZU3EG CPU Module with installed active heatsink, a base board and a SONY imx334 4K Sensor which is installed on the rear of the base board and connected to the MIPI-CSI interface through an FPC cable. From the CPU PL part, the board has extended one Gigabit Ethernet, one USB 3.0

device and one HDMI interface for

image output. From the PS part, the board has extended one USB-to-UART interface, one USB 3.0

Host, one TF card slot and one Gigabit Ethernet for data communication purpose. The board is

ready to run Linux operating system provided with plenty of

software resources.

MYIR also offer custom design services for board design based on the MYD-CZU3EG-ISP development board or customized image sensors or customized IP cores according to customers’ requirements.

The

built-in ISP core of the MYD-CZU3EG-ISP development board has excellent image processing

capabilities. It has outstanding intelligent noise reduction effect and can

separate from motion area and background accurately. The digital WDR function

and super 3D denoise technology of the ISP core can restore information from ultra-low

illuminance precisely. The automatic exposure strategy can be adopted according

to different usage scenarios and the color reduction is strong. The right images below are processed through

the IP cores of the MYD-CZU3EG-ISP development board which may make you feel the difference.

Image Effect Comparison

|

Features

|

Description

|

|

CPU

|

Xilinx Zynq UltraScale+ XCZU3EG-1SFVC784E (ZU3EG, 784 Pin Package) MPSoC

- 1.2GHz 64 bit Quad-core ARM® Cortex™-A53

- 600MHz Dual-core ARM® Cortex™-R5 proce

- ARM Mali™-400MP2 Graphics Processor

- 16nm FinFET+ FPGA fabric

|

|

RAM

|

4GB DDR4 SDRAM (64-bit, 2400MHz)

|

|

Flash

|

4GB eMMC, 128MB QSPI

|

|

PS Unit

|

One USB 3.0 Host

|

|

One USB-UART interface

|

|

One TF card slot

|

|

One 10/100/1000Mbps Ethernet interface

|

|

One 2.54mm pitch 14-pin JTAG interface (PS, PL reused)

|

|

PL Unit

|

One HDMI interface

|

|

One 10/100/1000Mbps Ethernet interface

|

|

One USB 3.0 device

|

|

One MIPI-CSI interface (0.5mm pitch 40-pin FPC connector, on the rear of the base board)

|

|

IO Expansion interface (0.5mm pitch 50-pin FPC connector, on the rear of the base board)

|

|

Image Sensor

SONY IMX334LLR

|

Resolution: 3840(H) x 2160 (V)

|

|

Mega Pixels: 8.42 MP

|

|

Frame Rate: 60 to 120 fps

|

|

ADC Resolution: 12-bit

|

|

Pixel Size: 2.0 μm × 2.0 μm

|

|

Interface: MIPI CSI-2

|

|

Dimensions

|

106.71mm x 69.98mm (base board)

|

|

Power supply

|

DC12V/2A

|

|

Working temp.

|

0~70 Celsius (commercial grade)

|

|

OS support

|

Linux 4.14.0

|

|

Target applications

|

IoT, Medical, Machine Vision, Industry, etc.

|

|

Packing List

|

One VECP Development Board

One HDMI cable

One 12V/2A Power

adapter

One Mini USB 2.0 cable

One 16GB TF card

One Product disk

|

Features of VECP Starter Kit

VECP Starter Kit in the Video

- $599 Xilinx ZYNQ UltraScale MPSoC VECP Kit with MIPI-CSI for image processing

- VECP Start Kit based on Zynq UltraScale+ MPSoC image output test

Other MYIR's Xilinx Products

http://www.myirtech.com/xilinxseries.asp

Z-turn Board Single Board Computer (based on Zynq-7010 / 7020)

Z-turn Lite Single Board Computer (based on Zynq-7007S / Zynq-7010)

MYD-C7Z015 Development Board (MYC-C7Z015 CPU Module as core board)

MYD-Y7Z010/20 Development Board (MYC-Y7Z010/20 CPU Module as core board)

MYD-C7Z010/20 Development Board (MYC-C7Z010/20 CPU Module as core board)

MYD-CZU3EG Development Board (MYC-CZU3EG CPU Module as core board)

MYD-CZU4EV Development Board (MYC-CZU4EV CPU Module as core board)

FZ3 Card - deep learning accelerator card (based on Xilinx Zynq UltraScale+ ZU3EG MPSoC)

|

Hardware Features

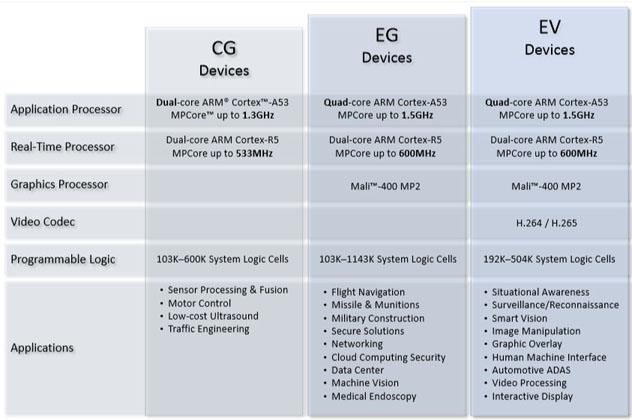

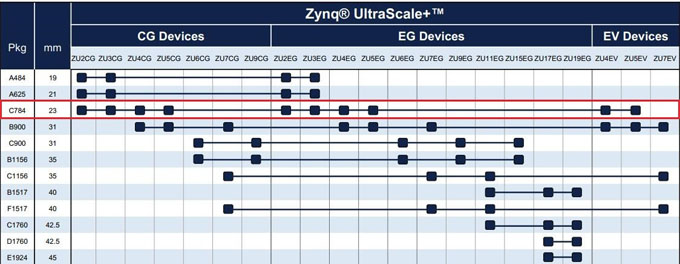

Zynq® UltraScale+™ MPSoC devices provide 64-bit processor scalability while combining real-time control with soft and hard engines for graphics, video, waveform, and packet processing. Built on a common real-time processor and programmable logic equipped platform, three distinct variants include dual application processor (CG) devices, quad application processor and GPU (EG) devices, and video codec (EV) devices.

Zynq UltraScale+ MPSoCs

The Zynq UltraScale+ family provides footprint compatibility to enable users to migrate designs from one device to another. Any two packages with the same footprint identifier code (last letter and number sequence) are footprint compatible. MYIR is using the XCZU3EG-1SFVC784E MPSoC for MYD-CZU3EG Development Board by default, the C784 package covers the widest footprint compatibilities that enable users to select devices among CG, EG and EV.

Zynq UltraScale+ MPSoC Device Migration Table

MYIR may also supply the MYC-CZU3EG CPU Modules with XCZU2CG, XCZU3CG, XCZU4EV or XCZU5EV MPSoC as options. The main features for the MPSoC devices are summarized as below.

|

Device

|

XCZU2CG

|

XCZU3CG

|

XCZU3EG

|

XCZU4EV

|

XCZU5EV

|

|

Logic cells (k)

|

103

|

154

|

154

|

192

|

256

|

|

CLB Flip-Flops (K)

|

94

|

141

|

141

|

176

|

234

|

|

CLB LUTs (K)

|

47

|

71

|

71

|

88

|

117

|

|

Block RAM (Mb)

|

5.3

|

7.6

|

7.6

|

4.5

|

5.1

|

|

UltraRAM (Mb)

|

-

|

-

|

-

|

13.5

|

18.0

|

|

DSP Slices

|

240

|

360

|

360

|

728

|

1,248

|

|

GTX transceivers

|

PS-GTR4x (6Gb/s)

|

PS-GTR4x (6Gb/s)

|

PS-GTR4x (6Gb/s)

|

PS-GTR4x (6Gb/s), GTH4x (16.3Gb/s)

|

PS-GTR4x (6Gb/s), GTH4x (16.3Gb/s)

|

|

Processor Units

|

|

Application Processor Unit

|

Dual-core ARM® Cortex™-A53 MPCore™ up to 1.3GHz

|

Quad-core ARM® Cortex™-A53 MPCore™ up to 1.5GHz

|

|

Memory w/ECC

|

L1 Cache 32KB I / D per core, L2 Cache 1MB, on-chip Memory 256KB

|

|

Real-Time Processor Unit

|

Dual-core ARM Cortex-R5 MPCore™ up to 600MHz

|

|

Memory w/ECC

|

L1 Cache 32KB I / D per core, Tightly Coupled Memory 128KB per core

|

|

Graphics Processing Unit

|

-

|

-

|

Mali™-400 MP2 up to 667MHz

|

|

Video Codec

|

-

|

-

|

-

|

H.264 / H.265

|

|

Memory L2 Cache

|

64KB

|

|

External Memory, Connectivity, Integrated Block Functionality

|

|

Dynamic Memory Interface

|

x32/x64: DDR4, LPDDR4, DDR3, DDR3L, LPDDR3 with ECC

|

|

Static Memory Interfaces

|

NAND, 2x Quad-SPI

|

|

High-Speed Connectivity

|

PCIe® Gen2 x4, 2x USB3.0, SATA 3.1, DisplayPort, 4x Tri-mode Gigabit Ethernet

|

|

General Connectivity

|

2 x USB 2.0, 2 x SD/SDIO, 2 x UART, 2 x CAN 2.0B, 2 x I2C, 2 x SPI, 4 x 32b GPIO

|

|

Power Management

|

Full / Low / PL / Battery Power Domains

|

|

Security

|

RSA, AES, and SHA

|

|

AMS - System Monitor

|

10-bit, 1MSPS – Temperature and Voltage Monitor

|

Zynq UltraScale+ MPSoC Device Selection Guide

Function Block Diagram of MYD-CZU3EG-ISP Development Board

|

Software Features

The MYD-CZU3EG-ISP Development Board is preloaded with Linux OS. MYIR provides software package in a product disk along with the goods delivery. The software package features as below:

|

Item

|

Features

|

Description

|

Remark

|

|

Cross compiler

|

gcc 7.2.1

|

gcc version 7.2.1 (Linaro

GCC7.2)

|

|

|

Boot program

|

BOOT.BIN

|

First boot program including FSBL, u-boot2018.01

|

Source code provided

|

|

Linux Kernel

|

Linux 4.14.0

|

Customized kernel for VECP Starter Kit

|

Source code provided

|

|

Drivers

|

USB Host

|

USB2.0/USB3.0 Host driver

|

Source code provided

|

|

Ethernet

|

Gigabit Ethernet driver

|

Source code provided

|

|

MMC/SD/TF

|

MMC/SD/TF card driver

|

Source code provided

|

|

Camera

|

Camera driver

|

Source code provided

|

|

HDMI

|

HDMI (SiI1136 X chip) driver

|

Source code provided

|

|

Button

|

Button driver

|

Source code provided

|

|

UART

|

UART driver

|

Source code provided

|

|

I2C

|

I2C driver

|

Source code provided

|

|

LED

|

LED driver

|

Source code provided

|

|

GPIO

|

GPIO driver

|

Source code provided

|

|

QSPI

|

QSPI Flash MT25QU512ABB driver

|

Source code provided

|

|

Watch dog

|

Watch dog driver

|

Source code provided

|

|

Applications

|

Net

|

Socket program

|

Source code provided

|

|

File System

|

Ramdisk

|

Ramdisk system image

|

File System

|

|

Rootfs.tar

|

Buildroot, including QT

|

Source code provided

|

Software Features of VECP Starter Kit

|

Relative Download and Links

You can download relative chip datasheet, products datasheet, user manual, software package from below. Detailed technical data available on request.

|

1

|

VECP Starter Kit Overview

|

984 KB

|

|

|

2

|

Zynq UltraScale+ MPSoC Product Selection Guide

|

1.88 MB

|

|

|

3

|

MYC-CZU3EG Pinouts Description

|

525 KB

|

|

|

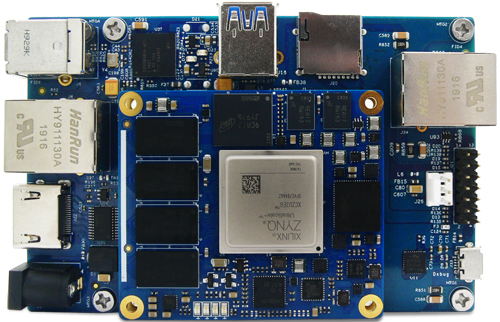

MYD-CZU3EG-ISP development board top-view (without active heatsink installed)

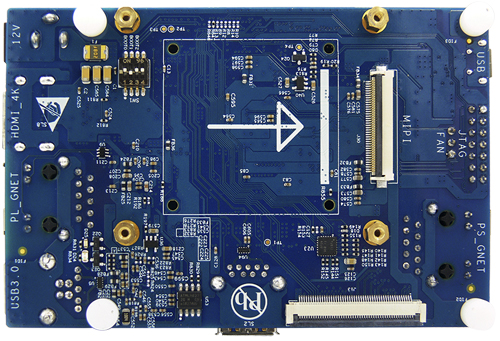

MYD-CZU3EG-ISP development board bottom-view (without image sensor installed)

|

Price and Ordering

|

Item

|

Packing List

|

Unit Price

|

Ordering

|

|

VECP Starter Kit

(Part No.: MYD-CZU3EG-4E4D-1200-C-ISP)

|

- One MYD-CZU3EG-ISP development board

(with active heatsink and image sensor)

- One 12V/2A Power Adapter

- One Mini USB Cable

- One 16GB TF Card

- One HDMI Cable

- One Product disk

(Including user manual, datasheet,

base board schematic in PDF format

and software packages)

|

USD599

|

|

|

MYD-CZU3EG-ISP Development Board

(Part No.: MYD-CZU3EG-4E4D-1200-C-ISP-S)

|

- One MYD-CZU3EG-ISP development board

(with active heatsink and image sensor)

|

Production recommended

Please inquire MYIR

|

|

Note:

We accept custom design based on the MYD-CZU3EG-ISP development board or customized image sensors or customized IP cores according to customers’ requirements. Please contact MYIR.

|

|

|

| |

|

|

|

|