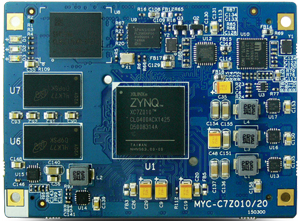

| Shenzhen, China - June 3, 2015 - MYIR introduced a low-cost System-on-Module MYC-C7Z010/20 based on Xilinx Zynq-7010 (XC7Z010-1CLG400C) or Zynq-7020 (XC7Z020-1CLG400C) SoC device which is among the Xilinx Zynq-7000 ARM Cortex-A9 processor with Xilinx 7-series Field Programmable Gate Array (FPGA) logic, capable of running at up to 866MHz. The module is measuring only 75mm by 55mm and integrates 1GB DDR3 SDRAM, 4GB eMMC, 32MB quad SPI Flash, a Gigabit Ethernet PHY, a USB PHY and external watchdog on board. Two 0.8mm pitch 140-pin board-to-board connectors provide a large number of I/O signals for ARM peripherals and FPGA I/Os to enable your base board extension.

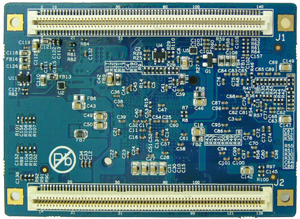

MYC-C7Z010/20 Top-view MYC-C7Z010/20 Bottom-view

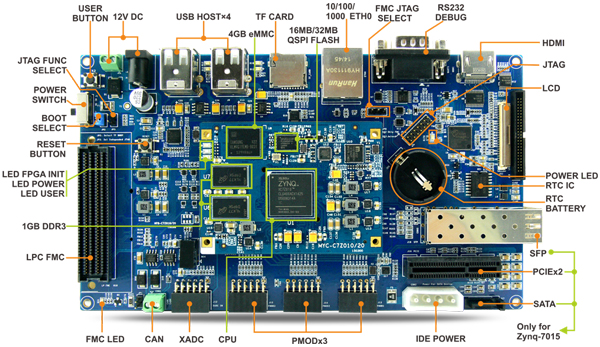

MYIR also offers a development board MYD-C7Z010/20 for evaluating or prototyping based on the MYC-C7Z010/20 CPU Module. It takes full features of the Zynq-7010 and Zynq-7020 SoCs’ powerful dual-core ARM Cortex-A9 processing system and Xilinx 7-series Field Programmable Gate Array

(FPGA) logic unit to create a rich set of peripherals to the base board through headers and connectors including one RS232 serial port, four USB Host ports, one Gigabit Ethernet port, CAN, HDMI, LCD/Touch, TF card

slot, RTC, one XADC header to allow you take advantage of Xilinx XADC; it has three PMoD headers to meet your I/O needs with PMoDs (only for 7020); it also has a low-pin count FMC connector to

allow various FMC cards for custom I/O options.

MYD-C7Z010/20 Development Board

The MYD-C7Z010/20 development board is delivered with necessary cable accessories and MYIR offers optional 4.3-inch and 7-inch LCD Module. It is an excellent starter kit for development based on Zynq-7000 family SoC.

|